From Surf Wiki (app.surf) — the open knowledge base

555 timer IC

Integrated circuit used for timer applications

Integrated circuit used for timer applications

| Field | Value | |

|---|---|---|

| name | 555 timer IC | |

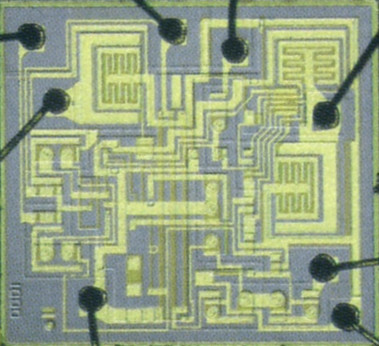

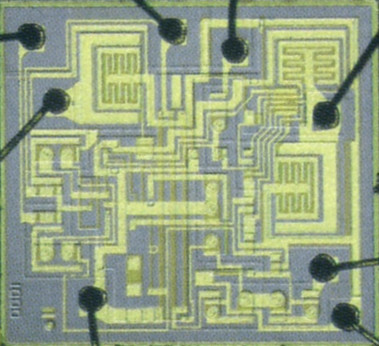

| image | Signetics NE555N.JPG | |

| image_size | 250 | |

| caption | Signetics NE555 in 8-pin DIP package | |

| type | Active, integrated circuit | |

| invented | Hans Camenzind (1971) | |

| first_produced | 1972 | |

| symbol | [[File:555 esquema.png | 250px]] |

| symbol_caption | Internal block diagram |

The 555 timer IC is an integrated circuit used in a variety of timer, delay, pulse generation, and oscillator applications. It is one of the most popular timing ICs due to its flexibility and price. Derivatives provide two (556) or four (558) timing circuits in one package. The design was first marketed in 1972 by Signetics and used bipolar junction transistors. Since then, numerous companies have made the original timers and later similar low-power CMOS timers. In 2017, it was said that over a billion 555 timers are produced annually by some estimates, and that the design was "probably the most popular integrated circuit ever made".

History

The timer IC was designed in 1971 by Hans Camenzind under contract to Signetics. In 1968, he was hired by Signetics to develop a phase-locked loop (PLL) IC. He designed an oscillator for PLLs such that the frequency did not depend on the power supply voltage or temperature. Signetics subsequently laid off half of its employees due to the 1970 recession, and development on the PLL was thus frozen. Camenzind proposed the development of a universal circuit based on the oscillator for PLLs and asked that he develop it alone, borrowing equipment from Signetics instead of having his pay cut in half. Camenzind's idea was originally rejected, since other engineers argued the product could be built from existing parts sold by the company; however, the marketing manager approved the idea.

The first design for the 555 was reviewed in the summer of 1971. After this design was tested and found to be without errors, Camenzind got the idea of using a direct resistance instead of a constant current source, finding that it worked satisfactorily. The design change decreased the required 9 external pins to 8, so the IC could be fit in an 8-pin package instead of a 14-pin package. This revised version passed a second design review, and the prototypes were completed in October 1971 as the NE555V (plastic DIP) and SE555T (metal TO-5). The 9-pin version had already been released by another company founded by an engineer who had attended the first review and had retired from Signetics; that firm withdrew its version soon after the 555 was released. The 555 timer was manufactured by 12 companies in 1972, and it became a best-selling product.

The 555 found many applications beyond timers. Camenzind noted in 1997 that "nine out of 10 of its applications were in areas and ways I had never contemplated. For months I was inundated by phone calls from engineers who had new ideas for using the device."

Name

Several books report the name "555" timer IC derived from the three 5 kΩ resistors inside the chip. However, in a recorded interview with an online transistor museum curator, Hans Camenzind said "It was just arbitrarily chosen. It was Art Fury (marketing manager) who thought the circuit was gonna sell big who picked the name '555' timer IC."

Design

Depending on the manufacturer, the standard 555 package incorporated the equivalent of 25 transistors, 2 diodes, and 15 resistors on a silicon chip packaged into an 8-pin dual in-line package (DIP-8). Variants available included the 556 (a DIP-14 combining two complete 555s on one chip), and 558 / 559 (both variants were a DIP-16 combining four reduced-functionality timers on one chip).

The NE555 parts were commercial temperature range, 0 °C to +70 °C, and the SE555 part number designated the military temperature range, −55 °C to +125 °C. These chips were available in both high-reliability metal can (T package) and inexpensive epoxy plastic (V package) form factors. Thus, the full part numbers were NE555V, NE555T, SE555V, and SE555T.

Low-power CMOS versions of the 555 are now available, such as the Intersil ICM7555 and Texas Instruments LMC555, TLC555, TLC551.

Internal schematic

The internal block diagram and schematic of the 555 timer are highlighted with the same color across all three drawings to clarify how the chip is implemented:

- : Between the positive supply voltage VCC and the ground GND is a voltage divider consisting of three identical resistors (5kΩ for bipolar timers, 100kΩ or higher for CMOS) to create reference voltages for the analog comparators. CONTROL is connected between the upper two resistors, allowing an external voltage to control the reference voltages:

- When CONTROL is not driven, this divider creates an upper reference voltage of VCC and a lower reference voltage of VCC.

- When CONTROL is driven, the upper reference voltage will instead be VCONTROL and the lower reference voltage will be VCONTROL.

- : The comparator's negative input is connected to voltage divider's upper reference voltage, and the comparator's positive input is connected to THRESHOLD.

- : The comparator's positive input is connected to voltage divider's lower reference, and the comparator's negative input is connected to TRIGGER.

- : A set-reset latch stores the state of the timer and is controlled by the two comparators. RESET overrides the other two inputs, thus the latch (and therefore the entire timer) can be reset at any time.

- : The output of the latch is followed by an output stage with pushpull output drivers that can supply up to 200mA for bipolar timers, lower for CMOS timers.

- : Also, the output of the latch controls a transistor acting as an electronic switch that connects DISCHARGE to ground.

File:NE555 Bloc Diagram.svg|555 internal block diagram File:NE555 Internal Circuit.svg|555 internal schematic of bipolar version File:C555 Internal Circuit.svg|555 internal schematic of CMOS version

Pinout

The pinout of the 8-pin 555 timer and 14-pin 556 dual timer are shown in the following table. Since the 556 is conceptually two 555 timers that share power pins, the pin numbers for each half are split across two columns.

| 555 pin# | 556 (unit 1) | 556 (unit 2) | Pin name | Pin direction | Pin description | |

|---|---|---|---|---|---|---|

| Ground supply: this pin is the ground reference voltage (zero volts). | ||||||

| Trigger: when *V*TRIGGER falls below *V*CONTROL ( *V*CC, except when CONTROL is driven by an external signal), OUTPUT goes to the high state and a timing interval starts. As long as TRIGGER continues to be kept at a low voltage, OUTPUT will remain in the high state. | ||||||

| Output: this pin is a push-pull (P.P.) output that is driven to either a low state (GND) or a high state (*V*CC minus approximately 1.7 volts for bipolar timers, or *V*CC for CMOS timers). | ||||||

| Reset: a timing interval may be reset by driving this pin to GND, but the timing does not begin again until this pin rises above approximately 0.7 volts. This pin overrides , which in turn overrides THRESHOLD. If this pin is not used, it should be connected to *V*CC to prevent electrical noise accidentally causing a reset. | ||||||

| Control: this pin provides access to the internal voltage divider ( *V*CC by default). By applying a voltage to this pin, the timing characteristics can be changed. In astable mode, this pin can be used to frequency-modulate the OUTPUT state. If this pin is not used, it should be connected to a 10 nF decoupling capacitor (between this pin and GND) to ensure electrical noise doesn't affect the internal voltage divider. | ||||||

| Threshold: when the voltage at this pin is greater than *V*CONTROL ( *V*CC by default except when CONTROL is driven by an external signal), then the OUTPUT high state timing interval ends, causing OUTPUT to go to the low state. | ||||||

| Discharge: This pin is an open-collector (O.C.) output for bipolar timers, or an open-drain (O.D.) output for CMOS timers. This pin can be used to discharge a capacitor when OUTPUT is low. In bistable latch and bistable inverter modes, this pin is unused, which allows it to be used as an alternate output. | ||||||

| Positive supply: For bipolar timers, the supply voltage range is typically 4.5 to 16 volts (some are spec'ed for up to 18 volts, though most will operate as low as 3 volts). For CMOS timers, the supply voltage range is typically 2 to 15 volts (some are spec'ed for up to 18 volts, and some are spec'ed as low as 1 volt). See the supply min and max columns in the derivatives table in this article. Decoupling capacitor(s) are generally applied (between this pin and GND) as a good practice. |

File:555 Pinout.svg| Pinout of 555 single timer File:NE556 pennen.svg| Pinout of 556 dual timer

Modes

The 555 IC has the following operating modes:

- Astable (free-running) mode – The 555 operates as an electronic oscillator. Applications include:

- As a general-purpose oscillator or clock/periodic timer, which may be used for many things including: Light emitting diode and lamp flashers, pulse generation, pulse-width modulation (PWM), logic clocks, tone generation, security alarms, pulse-position modulation, etc.

- Analog-to-digital conversion (ADC) from an analog value represented by a resistance or capacitance into a digital pulse length.

- e.g., selecting a thermistor as timing resistor allows the use of the 555 in a temperature sensor with the period of the output pulse determined by the temperature. A microprocessor can then convert the pulse period to temperature, linearize it, and even provide calibration.

- Monostable (one-shot) mode – The 555 operates as a "one-shot" pulse generator. Applications include:

- timers, missing pulse detection, bounce-free switches, touch switches, frequency dividers, triggered measurement of resistance or capacitance, PWM, etc.

- Bistable (latch) mode – The 555 operates as a set-reset latch. Applications include:

- switch debouncing.

- Schmitt trigger (inverter) mode – the 555 operates as a Schmitt trigger inverter gate. Application:

- Converts a noisy input into a clean digital output.

Astable

| Frequency | C | R1 | R2 | Duty cycle |

|---|---|---|---|---|

| 0.1Hz (+0.048%) | 100μF | 8.2kΩ | 68kΩ | 52.8% |

| 1Hz (+0.048%) | 10μF | 8.2kΩ | 68kΩ | 52.8% |

| 10Hz (+0.048%) | 1μF | 8.2kΩ | 68kΩ | 52.8% |

| 100Hz (+0.048%) | 100nF | 8.2kΩ | 68kΩ | 52.8% |

| 1kHz (+0.048%) | 10nF | 8.2kΩ | 68kΩ | 52.8% |

| 10kHz (+0.048%) | 1nF | 8.2kΩ | 68kΩ | 52.8% |

| 100kHz (+0.048%) | 100pF | 8.2kΩ | 68kΩ | 52.8% |

In the astable configuration, the 555 timer puts out a continuous stream of rectangular pulses having a specific period.

The astable configuration is implemented using two resistors, R_1 and R_2 , and one capacitor C. The threshold and trigger pins are both connected to the capacitor; thus they have the same voltage.

Its repeated operating cycle (starting with the capacitor uncharged) is:

- Since the capacitor's voltage will be below VCC, the trigger pin causes the 555's internal latch to change state, causing OUT to go high and the internal discharge transistor to cut-off.

- Since the discharge pin is no longer short-circuited to ground, the capacitor starts charging via current from Vcc through the resistors R_1 and R_2.

- Once the capacitor charge reaches Vcc, the threshold pin causes the 555's internal latch to change state, causing OUT to go low and the internal discharge transistor to go into saturation (maximal-conductivity) mode.

- This discharge transistor provides a discharge path, so the capacitor starts discharging through R_2.

- Once the capacitor's voltage drops below VCC, the cycle repeats from step 1.

During the first pulse, the capacitor charges from 0 V to VCC, however, in later pulses, it only charges from VCC to VCC. Consequently, the first pulse has a longer high time interval compared to later pulses. Moreover, the capacitor charges through both resistors but only discharges through R_2, thus the output high interval is longer than the low interval. This is shown in the following equations:

The output high time interval of each pulse is given by:

: t_\text{high} = \ln(2) \cdot (R_1 + R_2) \cdot C

The output low time interval of each pulse is given by:

: t_\text{low} = \ln(2) \cdot R_2 \cdot C

Hence, the frequency f of the pulse is given by:

: f = \frac{1}{t_\text{high} + t_\text{low}} = \frac{1}{\ln(2) \cdot (R_1 + 2 , R_2) \cdot C}

and the duty cycle D is given by:

: D~(%) = \frac{t_\text{high}}{t_\text{high} + t_\text{low}} \cdot 100 = \frac{R_1 + R_2}{R_1 + 2 , R_2} \cdot 100

where t is the time in seconds, R is the resistance in ohms, C is the capacitance in farads, and \ln(2) is the natural log of 2 constant.

Resistor R_1 requirements:

- Minimum resistance - it is recommended that 5 kiloohm be the minimum resistance for R_1, but this doesn't mean reasonable lower values can't be used in certain applications.

- Maximum resistance - a minimum threshold current of 0.25 microamp is required to trip the threshold comparator of a NE555 timer, thus resistance of R_1 should be limited to 6.6 megaohm when V_\text{CC} is 5 volts, or 20 megaohm when 15 volts. If capacitor C has significant leakage current, then the maximum resistance will need to be lowered to increase the charge current, otherwise R_1 will not be able to recharge the capacitor.

Shorter duty cycle

To create an output high time shorter than the low time (i.e., a duty cycle less than 50%) a fast diode (i.e. 1N4148 signal diode) can be placed in parallel with R2, with the cathode on the capacitor side. This bypasses R2 during the high part of the cycle, so that the high interval depends only on R1 and C, with an adjustment based on the voltage drop across the diode. The low time is unaffected by the diode and so remains \ln(2) , R_2 , C , . But the diode's forward voltage drop Vdiode slows charging on the capacitor, so the high time is longer than the often-cited \ln(2) , R_1 , C to become:

: t_\text{high} = \ln\left(\frac{2 , V_\text{CC} - 3 , V_\text{diode}}{V_\text{CC} - 3 , V_\text{diode}}\right) \cdot R_1 \cdot C,

where Vdiode is when the diode's "on" current is of VCC/R1 (which depends on the type of diode and can be found in datasheets or measured). When Vdiode is small relative to Vcc, this charging is faster and approaches \ln(2) , R_1 , C but is slower the closer Vdiode is to Vcc:

As an extreme example, when *V*CC = 5 V, and Vdiode = 0.7 V, high time is 1.00 R1C, which is 45% longer than the "expected" 0.693 R1C. At the other extreme, when *V*cc = 15 V, and Vdiode = 0.3 V, the high time is 0.725 R1C, which is closer to the expected 0.693 R1C. The equation approaches 0.693 R1C as *V*diode approaches 0 V.

Voltage-controlled pulse-width modulation

In the previous example schematics, the control pin was not used, thus it should connected to ground through a 10 nF decoupling capacitor to shunt electrical noise. However, if a time-varying voltage source was applied to the control pin, then the pulse widths would be dependent on the control voltage.

Monostable

Monostable mode produces an output pulse when the trigger signals drops below VCC. An RC circuit sets the output pulse's duration as the time t in seconds it takes to charge C to VCC:

: t = \ln(3) \cdot R \cdot C,

where R is the resistance in ohms, C is the capacitance in farads, \ln(3) is the natural log of 3 constant. The output pulse duration can be lengthened or shortened as desired by adjusting the values of R and C. Subsequent triggering before the end of this timing interval will not affect the output pulse.

Example values

| Time | C | R |

|---|---|---|

| 100 μs (−0.026%) | 1 nF | 91 kΩ |

| 1 ms (−0.026%) | 10 nF | 91 kΩ |

| 10 ms (−0.026%) | 100 nF | 91 kΩ |

| 100 ms (−0.026%) | 1 μF | 91 kΩ |

| 1 s (−0.026%) | 10 μF | 91 kΩ |

| 10 s (−0.026%) | 100 μF | 91 kΩ |

The timing table (right) shows common electronic component value solutions for various powers of 10 timings.

Scaling R and C by opposite powers of 10 will provide the same timing. For instance:

- 1ms ≅ 1nF and 910kΩ,

- 1ms ≅ 10nF and 91kΩ (values from table),

- 1ms ≅ 100nF and 9.1kΩ.

For each row in the example table (right), additional timing values can easily be created by adding one to three of the same resistor value in parallel and/or series. A second resistor in parallel, the new timing is half the table time. A second resistor in series, the new timing is double the table time.

- 2.5ms (0.25x) ≅ 100nF and 22.75kΩ (four 91kΩ resistors in parallel),

- 5ms (0.5x) ≅ 100nF and 45.5kΩ (two 91kΩ resistors in parallel),

- 10ms (1x) ≅ 100nF and 91kΩ (values from table),

- 15ms (1.5x) ≅ 100nF and 136.5kΩ (one 91kΩ resistor in series with "two 91kΩ resistors in parallel"),

- 20ms (2x) ≅ 100nF and 182kΩ (two 91kΩ resistors in series),

- 25ms (2.5x) ≅ 100nF and 227.5kΩ ("two 91kΩ resistors in series" in series with "two 91kΩ resistors in parallel"),

- 30ms (3x) ≅ 100nF and 273kΩ (three 91kΩ resistors in series),

- 40ms (4x) ≅ 100nF and 364kΩ (four 91kΩ resistors in series).

Bistable SR latch

A 555 timer can act as an active-low SR latch (though without an inverted output) with two outputs: output pin is a push-pull output, discharge pin is an open-collector output (requires a pull-up resistor).

For the schematic on the right, a input signal connects to the pin and connecting a input signal to the pin. Thus, pulling momentarily low acts as a "set" and transitions the output to the high state (VCC). Conversely, pulling momentarily low acts as a "reset" and transitions the Out pin to the low state (GND).

No timing capacitors are required in a bistable configuration. The threshold input is grounded because it is unused. The trigger and reset inputs may be held high via pull-up resistors if they are normally Hi-Z and only enabled by connecting to ground.

Bistable Schmitt trigger inverter gate

A 555 timer can be used to create a Schmitt trigger inverter gate with two outputs: output pin is a push-pull output, discharge pin is an open-collector output (requires a pull-up resistor).

For the schematic on the right, an input signal is AC-coupled through a low value series capacitor, then biased by identical high-resistance resistors R_1 and R_2, which causes the signal to be centered at Vcc. This centered signal is connected to both the trigger and threshold input pins of the timer. The input signal must be strong enough to excite the trigger levels of the comparators to exceed the lower VCC and upper VCC thresholds in order to cause them to change state, thus providing the Schmitt trigger feature.

No timing capacitors are required in a bistable configuration.

Packages

In 1972, Signetics originally released the 555 timer in DIP-8 and TO5-8 metal can packages, and the 556 timer was released in a DIP-14 package.

In 2006, the dual 556 timer was available in through-hole packages as DIP-14 (2.54 mm pitch), and surface-mount packages as SO-14 (1.27 mm pitch) and SSOP-14 (0.65 mm pitch).

In 2012, the 555 was available in through-hole packages as DIP-8 (2.54 mm pitch), and surface-mount packages as SO-8 (1.27 mm pitch), SSOP-8 / TSSOP-8 / VSSOP-8 (0.65 mm pitch), BGA (0.5 mm pitch).

The MIC1555 is a CMOS 555-type timer with three fewer pins available in SOT23-5 (0.95 mm pitch) surface-mount package.

Specifications

These specifications apply to the original bipolar NE555. Other 555 timers can have different specifications depending on the grade (industrial, military, medical, etc.).

| Operating temperature | 0 to 70 °C |

|---|

Derivatives

Numerous companies have manufactured one or more variants of the 555, 556, 558 timers over the past decades, under many different part numbers. The following is a partial list:

| Manufacturer | Part | |||||||

|---|---|---|---|---|---|---|---|---|

| number | Production | |||||||

| status | IC | |||||||

| process | Timers | |||||||

| total | Supply | |||||||

| min. (volt) | Supply | |||||||

| max. (volt) | *I*q (μA) | |||||||

| at 5 V | ||||||||

| supply | ||||||||

| Frequency | ||||||||

| max. (MHz) | class="unsortable" | Remarks | class="unsortable" | Datasheet | ||||

| Custom Silicon Solutions (CSS) | CSS555 | CMOS | 1 | 1.2 | 5.5 | 4.3 | 1.0 | |

| Diodes Inc | ZSCT1555 | Bipolar | 1 | 0.9 | 6 | 150 | 0.33 | |

| Japan Radio Company (JRC) | NJM555 | Bipolar | 1 | 4.5 | 16 | 3000 | 0.1* | |

| Microchip | MIC1555/7 | CMOS | 1* | 2.7 | 18 | 240 | 5.0* | |

| ON | MC1455 | Bipolar | 1 | 4.5 | 16 | 3000 | 0.1* | |

| Renesas | ICM7555 | CMOS | 1 | 2 | 18 | 40 | 1.0 | |

| Renesas | ICM7556 | CMOS | 2 | 2 | 18 | 80 | 1.0 | |

| **Signetics** | **NE555** | Bipolar | 1 | 4.5 | 16 | 3000 | 0.1* | |

| **Signetics** | **NE556** | Bipolar | 2 | 4.5 | 16 | 6000 | 0.1* | |

| **Signetics** | **NE558** | Bipolar | 4* | 4.5 | 16 | 4800* | 0.1* | |

| STMicroelectronics (ST) | TS555 | CMOS | 1 | 2 | 16 | 110 | 2.7 | |

| Texas Instruments (TI) | LM555 | Bipolar | 1 | 4.5 | 16 | 3000 | unspecified | |

| Texas Instruments | LM556 | Bipolar | 2 | 4.5 | 16 | 6000 | 0.1 | |

| Texas Instruments | LMC555 | CMOS | 1 | 1.5 | 15 | 100 | 3.0 | |

| Texas Instruments | NE555 | Bipolar | 1 | 4.5 | 16 | 3000 | 0.1* | |

| Texas Instruments | NE556 | Bipolar | 2 | 4.5 | 16 | 6000 | 0.1* | |

| Texas Instruments | TLC551 | CMOS | 1 | 1 | 15 | 170 | 1.8 | |

| Texas Instruments | TLC552 | CMOS | 2 | 1 | 15 | 340 | 1.8 | |

| Texas Instruments | TLC555 | CMOS | 1 | 2 | 15 | 170 | 2.1 | |

| Texas Instruments | TLC556 | CMOS | 2 | 2 | 15 | 340 | 2.1 | |

| X-REL | XTR655 | SOI | 1 | 2.8 | 5.5 | 170 | 4.0 |

; Table notes

- All information in the above table was pulled from references in the datasheet column, except where denoted below.

- For the "Total timers" column, a "*" denotes parts that are missing 555 timer features.

- For the "Iq" column, a 5-volt supply was chosen as a common voltage to make it easier to compare. The value for Signetics NE558 is an estimate because NE558 datasheets don't state Iq at 5 V. The value listed in this table was estimated by comparing the 5 V to 15 V ratio of other bipolar datasheets, then derating the 15 V parameter for the NE558 part, which is denoted by the "*".

- For the "Frequency max." column, a "*" denotes values that may not be the actual maximum frequency limit of the part. The MIC1555 datasheet discusses limitations from 1 to 5 MHz. Though most bipolar timers don't state the maximum frequency in their datasheets, they all have a maximum frequency limitation of hundreds of kHz across their full temperature range. Section 8.1 of the Texas Instruments NE555 datasheet states a value of 100 kHz, and their website shows a value of 100 kHz in timer comparison tables. Signetics App Note 170 states that most devices will oscillate up to 1 MHz; however, when considering temperature stability, it should be limited to about 500 kHz. The application note from HFO mentions that at higher supply voltages the maximum power dissipation of the circuit might limit the operating frequency, as the supply current increases with frequency.

- For the "Manufacturer" column, the following associates historical 555 timer manufacturers to current company names.

- Fairchild Semiconductor was sold to ON Semiconductor in 2016. ON Semiconductor was founded in 1999 as a spinoff of Motorola Semiconductor Components Group. The MC1455 started as a Motorola product.

- Intersil was sold to Renesas Electronics in 2017. The ICM7555 and ICM7556 started as Intersil products.

- Micrel was sold to Microchip Technology in 2015. The MIC1555 started as a Micrel product.

- National Semiconductor was sold to Texas Instruments in 2011. The LM555 and LM556 started as a National Semiconductor products.

- Signetics was sold to Philips Semiconductor in 1975, later to NXP Semiconductors in 2006.

- Zetex Semiconductors was sold to Diodes Incorporated in 2008. The ZSCT1555 started as a Zetex product.

556 dual timer

The dual version is called 556. It features two complete 555 timers in a 14-pin package; only the two power-supply pins are shared between the two timers. In 2020, the bipolar version was available as the NE556, and the CMOS versions were available as the Intersil ICM7556 and Texas Instruments TLC556 and TLC552. See derivatives table in this article.

558 quad timer

The quad version is called 558 and has four reduced-functionality timers in a 16-pin package designed primarily for monostable multivibrator applications. By 2014, many versions of 16-pin NE558 have become obsolete.

Partial list of differences between 558 and 555 chips:

- One VCC and one GND, similar to 556 chip.

- Four "Reset" are tied together internally to one external pin (558).

- Four "Control Voltage" are tied together internally to one external pin (558).

- Four "Triggers" are falling-edge sensitive (558), instead of level sensitive (555).

- Two resistors in the voltage divider (558), instead of three resistors (555).

- One comparator (558), instead of two comparators (555).

- Four "Output" are open-collector (O.C.) type (558), instead of push–pull (P.P.) type (555).

Notes

References

References

- (15 August 2012). "Hans Camenzind, 555 timer inventor, dies". EE Times.

- Lowe, Doug. (2017-02-06). "Electronics All-in-One For Dummies". Wiley.

- Carmenzind, Hans. (2010). "タイマIC 555 誕生秘話". CQ出版.

- Santo, Brian. (May 2009). "25 Microchips That Shook the World". IEEE Spectrum.

- Ward, Jack. (2004). "The 555 Timer IC – An Interview with Hans Camenzind". The Semiconductor Museum.

- (2016). "Practical Electronics for Inventors". McGraw Hill.

- Kleitz, William. (1990). "Digital electronics : a practical approach". Prentice Hall.

- Simpson, Colin D.. (1996). "Industrial electronics". Prentice Hall.

- GoldStein, Harry. (March 3, 2003). "The Irresistible Transistor". IEEE Spectrum.

- "Oral History Hans Camenzind Historic 555 IC Page2". The Semiconductor Museum.

- "Oral History Hans Camenzind Historic 555 Integrated Circuit Page6".

- (1974). "TTL Cookbook". Sams.

- (1977). "IC Timer Cookbook". Sams Publishing.

- Carr, Joseph. (1996-12-19). "Linear IC Applications: A Designer's Handbook". Newnes.

- Buiting, Jan. (2003). "308 Circuits". Elektor International Media.

- (June 19, 2015). "555 Timer as Schmitt Trigger".

- (July 2012). "CSS555 Datasheet".

- "CSS555 Part Search".

- Senft, James. (February 2016). "The Remarkable CSS555". Nuts & Volts Magazine.

- (July 2006). "ZSCT1555 Datasheet".

- (November 2012). "NJM555 Datasheet".

- (March 2017). "MIC1555 Datasheet".

- (December 2009). "MC1455 Datasheet".

- (June 2016). "ICM7555-556 Datasheet".

- (1972). "Linear Vol1 Databook".

- (1973). "555/556 Timers Databook".

- (1979). "Analog Applications Manual".

- (1985). "Linear LSI Data and Applications Manual".

- (June 2015). "TS555 Datasheet".

- (January 2015). "LM555 Datasheet".

- (October 2015). "LM556 Datasheet".

- (July 2016). "LMC555 Datasheet".

- (September 2014). "NE555 Datasheet".

- (June 2006). "NE556 Datasheet".

- (September 1997). "TLC551 Datasheet".

- (May 1988). "TLC552 Datasheet".

- (August 2016). "TLC555 Datasheet".

- (September 1997). "TLC556 Datasheet".

- (August 2021). "XTR655 Datasheet".

- Reick, Ullrich. (1986-03-01). "Zeitgeber-IS B 555 / B 556". Halbleiterwerk Frankfurt (Oder).

- (September 19, 2016). "ON Semiconductor Successfully Completes Acquisition of Fairchild Semiconductor".

- (August 5, 1999). "Former Motorola group emerges as ON Semiconductor". [[EE Times]].

- (February 22, 2017). "Renesas and Intersil Announce Final Regulatory Approval for Renesas' Acquisition of Intersil".

- (August 12, 2015). "Microchip Technology Completes Micrel Acquisition".

- (September 23, 2011). "Texas Instruments completes acquisition of National Semiconductor".

- (2008). "NXP Semiconductors history".

- (June 13, 2008). "Diodes Incorporated closes acquisition of Zetex".

- Camenzind, H.R.. (September 1997). "Redesigning the old 555 [timer circuit]". IEEE Spectrum.

- Horn, Delton. (1994). "Amplifiers, waveform generators, and other low-cost IC projects". TAB Books.

- (2014-11-13). "LEDs, LCDs, Audio, Thyristors, Digital Logic, and Amplification". Maker Media.

This article was imported from Wikipedia and is available under the Creative Commons Attribution-ShareAlike 4.0 License. Content has been adapted to SurfDoc format. Original contributors can be found on the article history page.

Ask Mako anything about 555 timer IC — get instant answers, deeper analysis, and related topics.

Research with MakoFree with your Surf account

Create a free account to save articles, ask Mako questions, and organize your research.

Sign up freeThis content may have been generated or modified by AI. CloudSurf Software LLC is not responsible for the accuracy, completeness, or reliability of AI-generated content. Always verify important information from primary sources.

Report